# DS2155 T1/E1/J1 Single-Chip Transceiver

#### www.maxim-ic.com

#### **GENERAL DESCRIPTION**

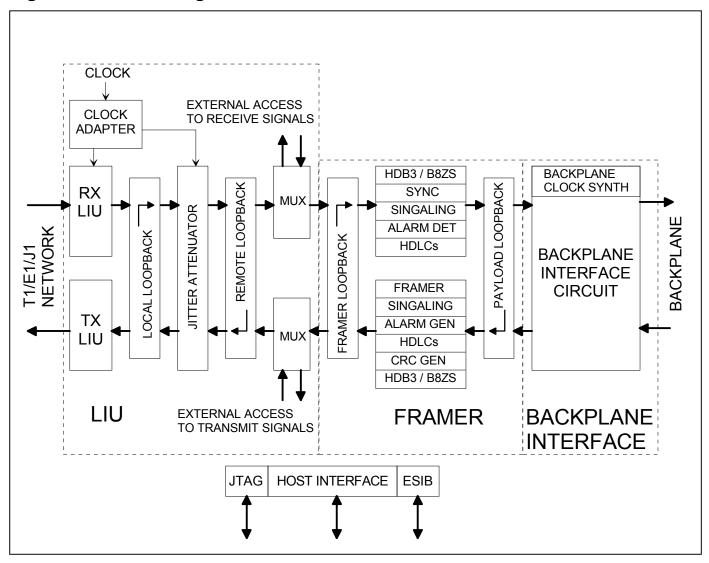

The DS2155 is a software-selectable T1, E1, or J1 single-chip transceiver (SCT) for short-haul and long-haul applications. The DS2155 is composed of a line interface unit (LIU), framer, HDLC controllers, and a TDM backplane interface, and is controlled by an 8-bit parallel port configured for Intel or Motorola bus operations. The DS2155 is pin and software compatible with the DS2156.

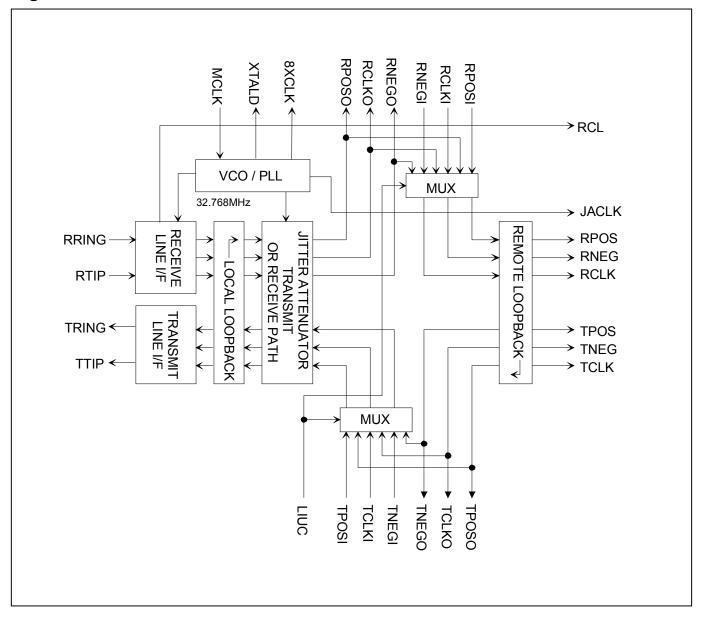

The LIU is composed of transmit and receive interfaces and a jitter attenuator. The transmit interface is responsible for generating the necessary waveshapes for driving the network and providing the correct source impedance depending on the type of media used. T1 waveform generation includes DSX-1 line buildouts as well as CSU line buildouts of -7.5dB, -15dB, and -22.5dB. E1 waveform generation includes G.703 waveshapes for both  $75\Omega$  coax and  $120\Omega$  twisted cables. The receive interface provides network termination and recovers clock and data from the network.

### **APPLICATIONS**

T1/E1/J1 Line Cards Switches and Routers Add-Drop Multiplexers

### **FEATURES**

- Complete T1/DS1/ISDN-PRI/J1 Transceiver Functionality

- Complete E1 (CEPT) PCM-30/ISDN-PRI Transceiver Functionality

- Long-Haul and Short-Haul Line Interface for Clock/Data Recovery and Waveshaping

- CMI Coder/Decoder for Optical I/F

- Crystal-Less Jitter Attenuator

- Fully Independent Transmit and Receive Functionality

- Dual HDLC Controllers

- Programmable BERT Generator and Detector

- Internal Software-Selectable Receive and Transmit-Side Termination Resistors for 75Ω/100Ω/120Ω T1 and E1 Interfaces

- Dual Two-Frame Elastic-Store Slip Buffers that Connect to Asynchronous Backplanes Up to 16.384MHz

- 16.384MHz, 8.192MHz, 4.096MHz, or 2.048MHz Clock Output Synthesized to Recovered Network Clock

Features continued in Section 3.

#### ORDERING INFORMATION

| PART      | TEMP RANGE                       | PIN-PACKAGE |

|-----------|----------------------------------|-------------|

| DS2155L   | $0^{\circ}$ C to $+70^{\circ}$ C | 100 LQFP    |

| DS2155L+  | $0^{\circ}$ C to $+70^{\circ}$ C | 100 LQFP    |

| DS2155LN  | -40°C to +85°C                   | 100 LQFP    |

| DS2155LN+ | -40°C to +85°C                   | 100 LQFP    |

| DS2155G   | $0^{\circ}$ C to $+70^{\circ}$ C | 100 CSBGA   |

| DS2155G+  | $0^{\circ}$ C to $+70^{\circ}$ C | 100 CSBGA   |

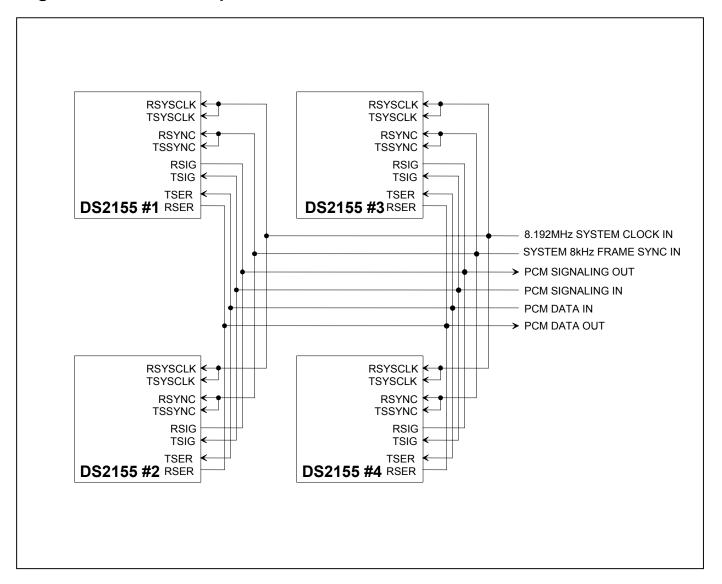

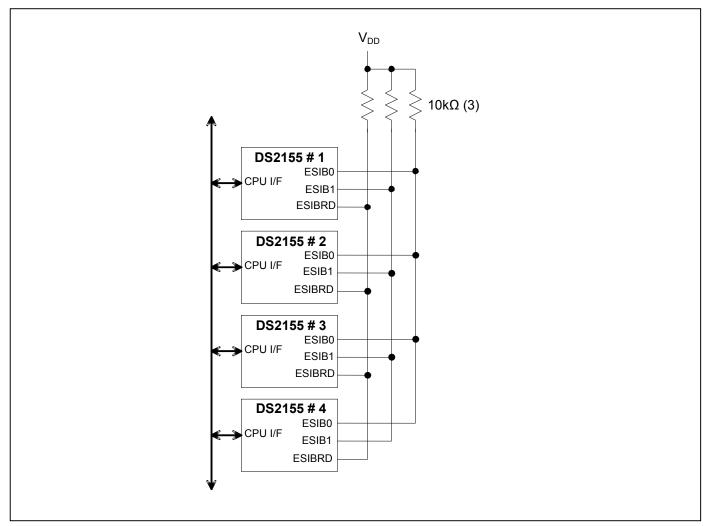

| DS2155GN  | -40°C to +85°C                   | 100 CSBGA   |

| DS2155GN  | -40°C to +85°C                   | 100 CSBGA   |

<sup>+</sup> Denotes a lead-free/RoHS-compliant package.

**Note:** Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device may be simultaneously available through various sales channels. For information about device errata, click here: <a href="https://www.maxim-ic.com/errata">www.maxim-ic.com/errata</a>.

1 of 238 REV: 080607

## 1. TABLE OF CONTENTS

| 1.         | TABLE OF CONTENTS                                 | 2  |

|------------|---------------------------------------------------|----|

| 1.1        | TABLE OF FIGURES                                  | 6  |

| 1.2        | TABLE OF TABLES.                                  | 7  |

| 2.         | DATA SHEET REVISION HISTORY                       | 8  |

| 3.         | MAIN FEATURES                                     | 10 |

| 3.1        | FUNCTIONAL DESCRIPTION                            | 13 |

| 3.2        | BLOCK DIAGRAM                                     |    |

| 4.         | PIN FUNCTION DESCRIPTION                          | 19 |

| 4.1        | Transmit Side                                     | 19 |

| 4.2        | RECEIVE SIDE                                      |    |

| 4.3        | PARALLEL CONTROL PORT PINS                        |    |

| 4.4        | EXTENDED SYSTEM INFORMATION BUS                   |    |

| 4.5        | USER OUTPUT PORT PINS                             |    |

| 4.6        | JTAG TEST ACCESS PORT PINS                        |    |

| 4.7<br>4.8 | LINE INTERFACE PINS                               |    |

| 4.8<br>4.9 | L AND G PACKAGE PINOUT                            |    |

| 4.10       | 10mm CSBGA PIN CONFIGURATION                      |    |

| 5.         | PARALLEL PORT                                     |    |

| 5.1        | REGISTER MAP                                      | 33 |

| 6.         | PROGRAMMING MODEL                                 | 39 |

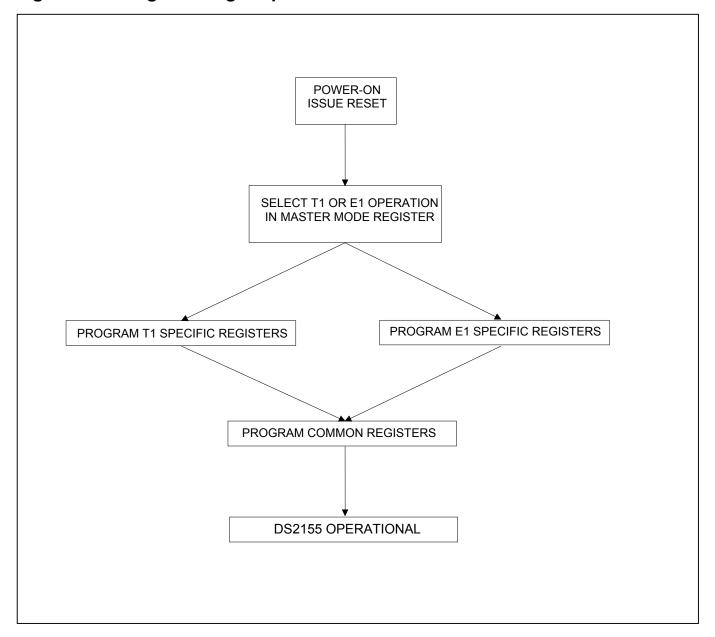

| 6.1        | POWER-UP SEQUENCE                                 | 40 |

| 6.1        | · · · · · · · · · · · · · · · · · · ·             |    |

| 6.2        | INTERRUPT HANDLING                                |    |

| 6.3        | STATUS REGISTERS.                                 |    |

| 6.4        | Information Registers                             |    |

| 6.5        | INTERRUPT INFORMATION REGISTERS                   | 42 |

| 7.         | SPECIAL PER-CHANNEL REGISTER OPERATION            | 43 |

| 8.         | CLOCK MAP                                         | 45 |

| 9.         | T1 FRAMER/FORMATTER CONTROL AND STATUS REGISTERS  | 46 |

| 9.1        | T1 CONTROL REGISTERS                              |    |

| 9.1        | T1 TRANSMIT TRANSPARENCY                          |    |

| 9.3        | AIS-CI AND RAI-CI GENERATION AND DETECTION        |    |

| 9.4        | T1 RECEIVE-SIDE DIGITAL-MILLIWATT CODE GENERATION |    |

| 10.        | E1 FRAMER/FORMATTER CONTROL AND STATUS REGISTERS  | 55 |

| 10.1       | E1 CONTROL REGISTERS                              | 55 |

| 10.2       | AUTOMATIC ALARM GENERATION                        |    |

| 10.3       | E1 Information Registers                          |    |

| 11.        | COMMON CONTROL AND STATUS REGISTERS               | 62 |

| 11.1       | T1/E1 STATUS REGISTERS                            | 63 |

| 12.                 | I/O PIN CONFIGURATION OPTIONS                                    | 69  |

|---------------------|------------------------------------------------------------------|-----|

| 13.                 | LOOPBACK CONFIGURATION                                           | 71  |

| 13.1                | PER-CHANNEL LOOPBACK                                             | 73  |

| 14.                 | ERROR COUNT REGISTERS                                            | 75  |

| 14.1                | LINE-CODE VIOLATION COUNT REGISTER (LCVCR)                       | 76  |

| 14                  | 4.1.1 T1 Operation                                               |     |

| 14                  | 4.1.2 E1 Operation                                               |     |

| 14.2                | Titin cobb (Tobilitor, Coord Tesos Per (To (Cor)                 |     |

|                     | 4.2.1 T1 Operation                                               |     |

| $\frac{14.3}{14.3}$ | 4.2.2 E1 Operation                                               |     |

|                     | ,                                                                |     |

|                     | 4.3.1 T1 Operation                                               |     |

| 14.4                |                                                                  |     |

| 15.                 | DS0 MONITORING FUNCTION                                          |     |

| 16.                 | SIGNALING OPERATION                                              | 83  |

| 16.1                |                                                                  |     |

|                     | 6.1.1 Processor-Based Signaling                                  |     |

|                     | 6.1.2 Hardware-Based Receive Signaling                           |     |

| 16.2                |                                                                  |     |

| 10                  | 5.2.1 Processor-Based Mode                                       |     |

| 10                  | 6.2.2 Software Signaling Insertion-Enable Registers, E1 CAS Mode | 93  |

| 10                  | 5.2.3 Software Signaling Insertion-Enable Registers, T1 Mode     | 95  |

| 10                  | 5.2.4 Hardware-Based Mode                                        | 95  |

| 17.                 | PER-CHANNEL IDLE CODE GENERATION                                 | 96  |

| 17.1                | IDLE-CODE PROGRAMMING EXAMPLES                                   | 97  |

| 18.                 | CHANNEL BLOCKING REGISTERS                                       | 101 |

| 19.                 | ELASTIC STORES OPERATION                                         | 104 |

| 19.1                | RECEIVE SIDE                                                     | 107 |

| 19                  | 9.1.1 T1 Mode                                                    | 107 |

| 19                  | 9.1.2 E1 Mode                                                    | 107 |

| 19.2                |                                                                  |     |

|                     | 9.2.1 T1 Mode                                                    |     |

|                     | 9.2.2 E1 Mode                                                    |     |

| 19.3                |                                                                  |     |

| 19.4                |                                                                  |     |

| 20.                 | G.706 INTERMEDIATE CRC-4 UPDATING (E1 MODE ONLY)                 |     |

| 21.                 | T1 BIT-ORIENTED CODE (BOC) CONTROLLER                            |     |

| 21.1                | Transmit BOC                                                     | 110 |

|                     | ransmit a BOC                                                    |     |

| 21.2                |                                                                  |     |

| $R_0$               | eceive a BOC                                                     | 110 |

| 22                  | ADDITIONAL (SA) AND INTERNATIONAL (SI) DIT OPERATION (ELONI V)   | 112 |

| 22.1         | METHOD 1: HARDWARE SCHEME                                   | 113   |

|--------------|-------------------------------------------------------------|-------|

| 22.2         | METHOD 2: INTERNAL REGISTER SCHEME BASED ON DOUBLE-FRAME    |       |

| 22.3         | METHOD 3: INTERNAL REGISTER SCHEME BASED ON CRC4 MULTIFRAME | 116   |

| 23. I        | HDLC CONTROLLERS                                            | 126   |

| 23.1         | BASIC OPERATION DETAILS                                     | 126   |

| 23.2         | HDLC CONFIGURATION                                          | 126   |

| 23.2         | .1 FIFO Control                                             | 130   |

| 23.3         | HDLC MAPPING                                                | 131   |

| 23.3         |                                                             |       |

| 23.3         |                                                             |       |

| 23.3         |                                                             |       |

| 23.3         |                                                             |       |

| 23.3         |                                                             |       |

| 23.4         | RECEIVE HDLC CODE EXAMPLE                                   |       |

| 23.5         | LEGACY FDL SUPPORT (T1 MODE)                                |       |

| 23.5         |                                                             |       |

| 23.5         |                                                             |       |

| 23.5         |                                                             |       |

| 23.6         | D4/SLC-96 OPERATION                                         |       |

| 24. I        | LINE INTERFACE UNIT (LIU)                                   |       |

| 24.1         | LIU OPERATION                                               |       |

| 24.2         | Receiver                                                    |       |

| 24.2         |                                                             |       |

| 24.2         | , , , , , , , , , , , , , , , , , , , ,                     |       |

| 24.2         |                                                             |       |

| 24.3         | TRANSMITTER                                                 |       |

| 24.3         |                                                             |       |

| 24.3<br>24.3 | 1                                                           |       |

| 24.3<br>24.3 |                                                             |       |

| 24.3<br>24.4 | .4 Transmit G.703 Synchronization Signal (E1 Mode)          |       |

| 24.4         | JITTER ATTENUATOR                                           |       |

| 24.6         | CMI (CODE MARK INVERSION) OPTION                            |       |

| 24.7         | LIU Control Registers                                       |       |

| 24.8         | RECOMMENDED CIRCUITS                                        |       |

| 24.9         | COMPONENT SPECIFICATIONS                                    |       |

|              | PROGRAMMABLE IN-BAND LOOP CODE GENERATION AND DETECTION     |       |

| 23. I        | ROGRAMMABLE IN-BAND LOOF CODE GENERATION AND DETECTION      | 103   |

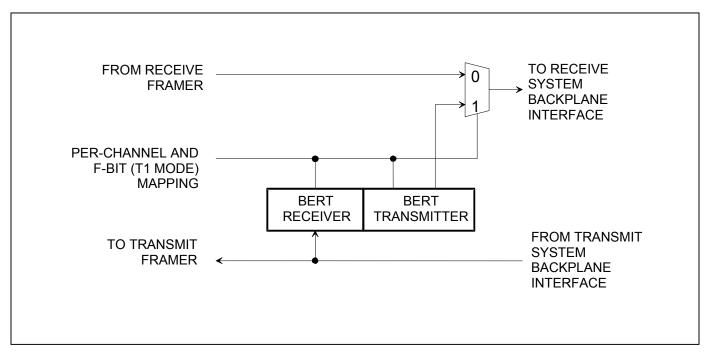

| 26. I        | BERT FUNCTION                                               | 170   |

| 26.1         | Status                                                      | 170   |

| 26.2         | MAPPING                                                     | 170   |

| 26.3         | BERT REGISTER DESCRIPTIONS                                  | 172   |

| 26.4         | BERT REPETITIVE PATTERN SET                                 | 176   |

| 26.5         | BERT BIT COUNTER                                            | 177   |

| 26.6         | BERT Error Counter                                          | 178   |

| 27. I        | PAYLOAD ERROR-INSERTION FUNCTION (T1 MODE ONLY)             | 180   |

| 27.1         | Number-of-Errors Registers                                  |       |

| 27.1         |                                                             |       |

|              | INTERLEAVED PCM RUS OPERATION (IRO)                         |       |

| /X           | INTERTEAVED PUWIKUS OPERATUW (IKO)                          | 1 🗙 🗸 |

| 28.1                                 | CHANNEL INTERLEAVE                                                                                                                                                                  |                   |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 28.2                                 | Frame Interleave                                                                                                                                                                    |                   |

| 29.                                  | EXTENDED SYSTEM INFORMATION BUS (ESIB)                                                                                                                                              | 187               |

| 30.                                  | PROGRAMMABLE BACKPLANE CLOCK SYNTHESIZER                                                                                                                                            | 191               |

| 31.                                  | FRACTIONAL T1/E1 SUPPORT                                                                                                                                                            | 191               |

| 32.                                  | USER-PROGRAMMABLE OUTPUT PINS                                                                                                                                                       | 193               |

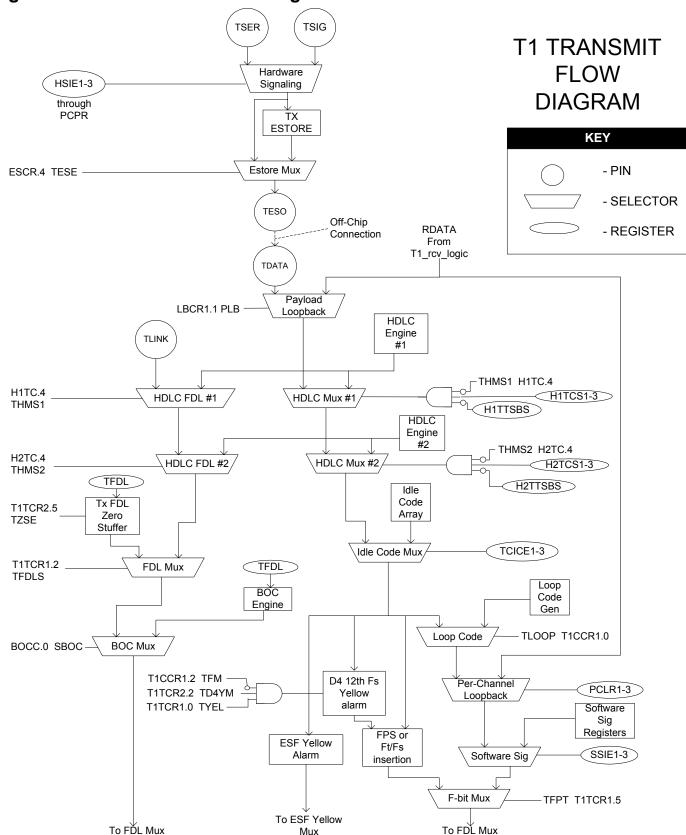

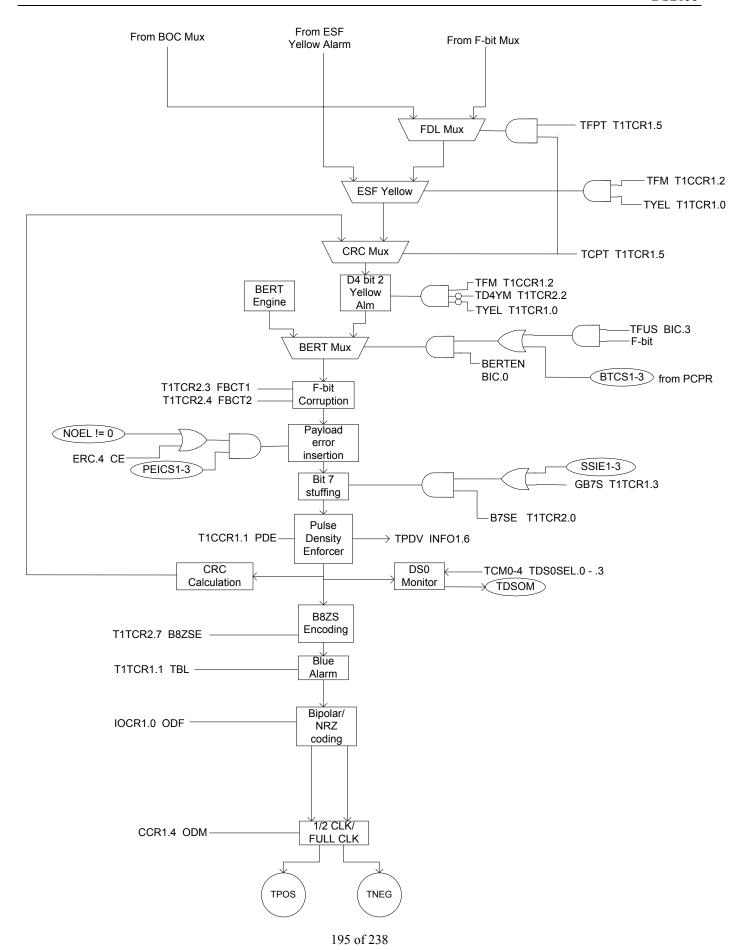

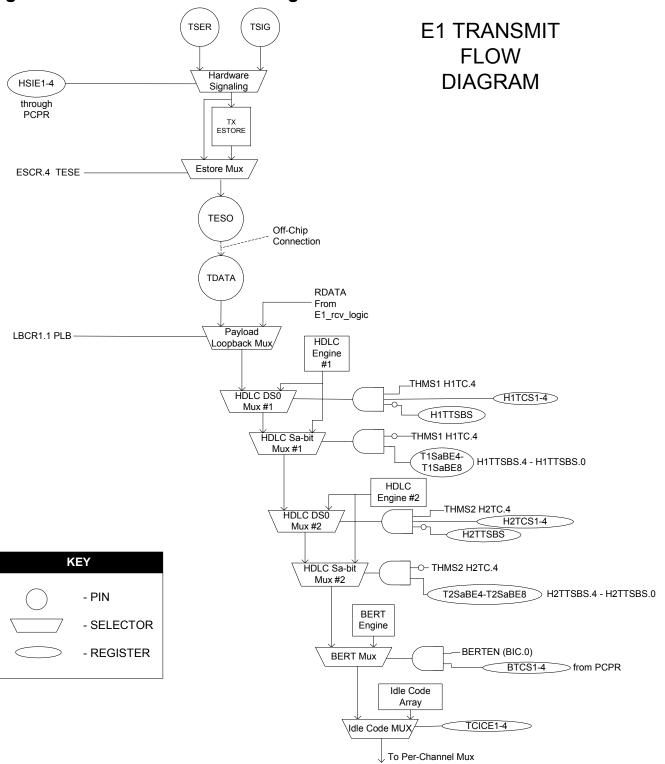

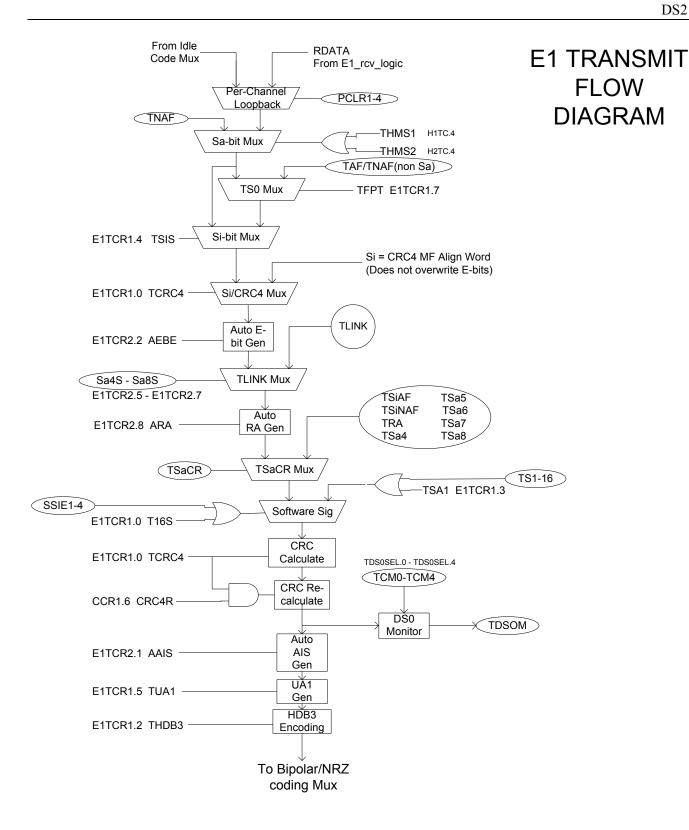

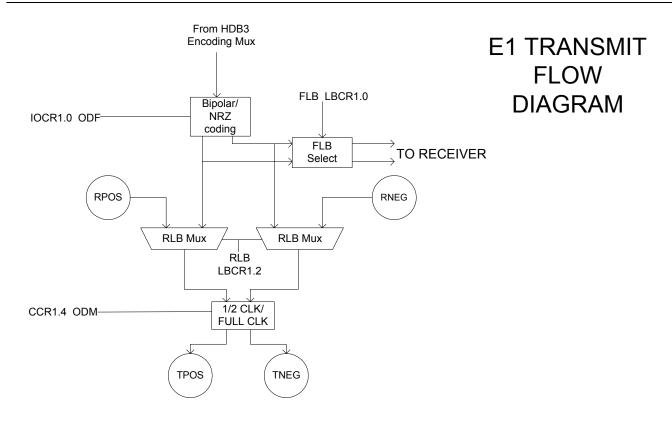

| 33.                                  | TRANSMIT FLOW DIAGRAMS                                                                                                                                                              | 194               |

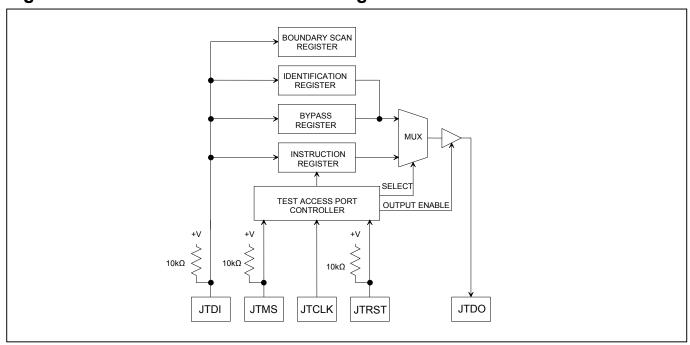

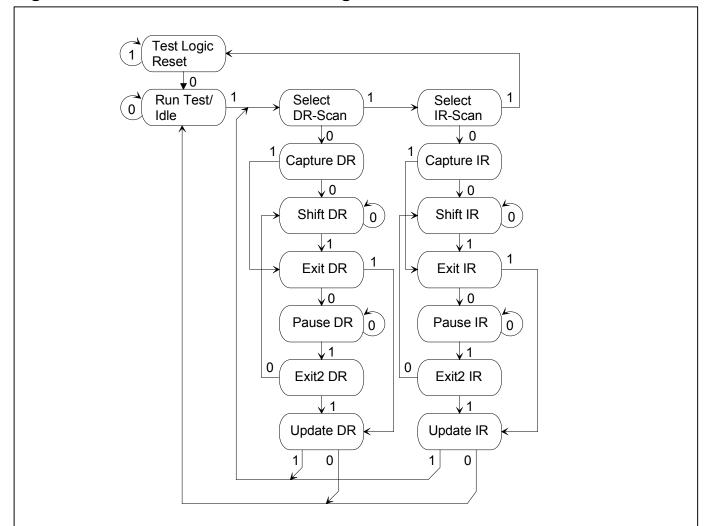

| 34.                                  | JTAG BOUNDARY SCAN ARCHITECTURE AND TEST ACCESS PORT                                                                                                                                | 199               |

| 34.1<br>34.2<br>34.3                 | DESCRIPTION INSTRUCTION REGISTER TEST REGISTERS                                                                                                                                     | 202               |

| 34.4<br>34.5<br>34.6                 | BOUNDARY SCAN REGISTER BYPASS REGISTER IDENTIFICATION REGISTER                                                                                                                      | 204<br>204        |

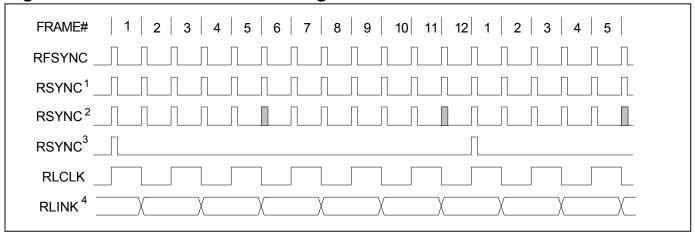

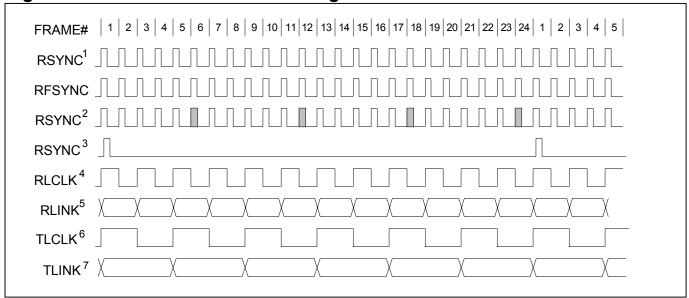

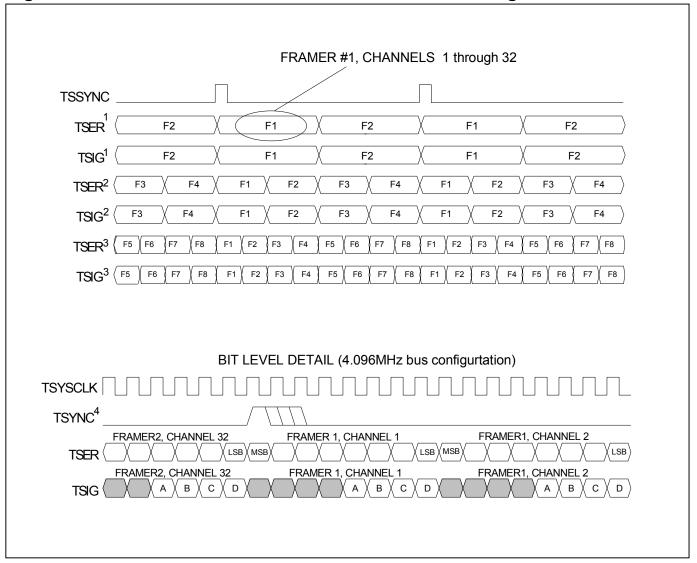

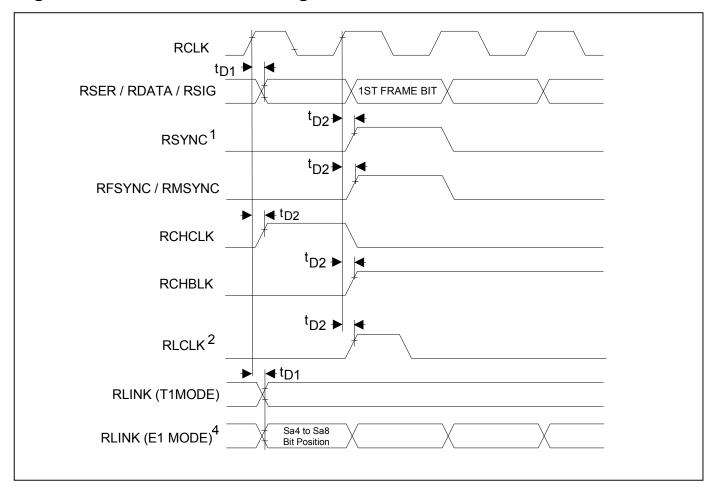

| 35.                                  | FUNCTIONAL TIMING DIAGRAMS                                                                                                                                                          | 208               |

| 35.1<br>35.2                         | T1 ModeE1 Mode                                                                                                                                                                      |                   |

| 36.                                  | OPERATING PARAMETERS                                                                                                                                                                | 222               |

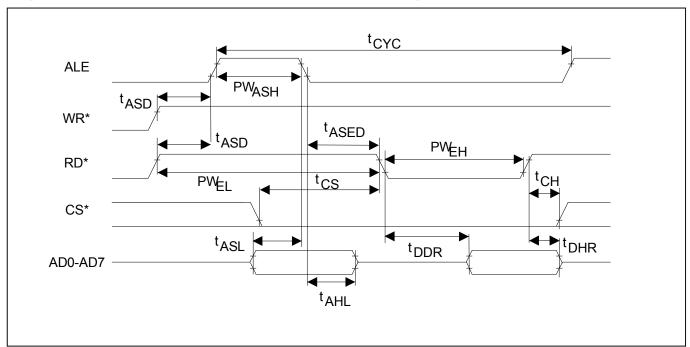

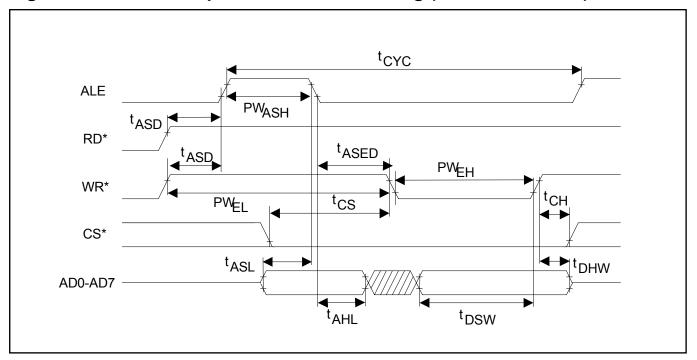

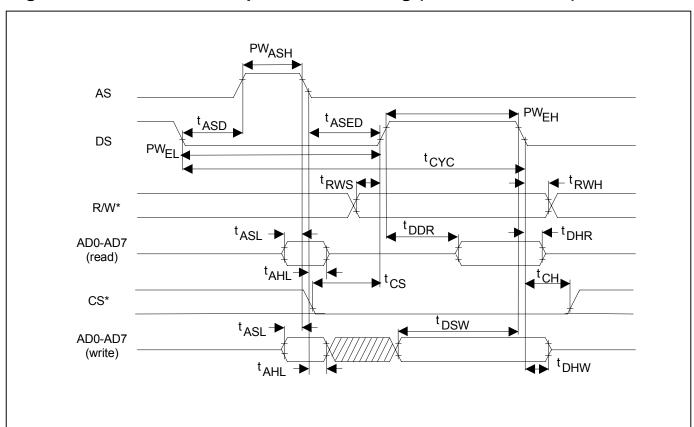

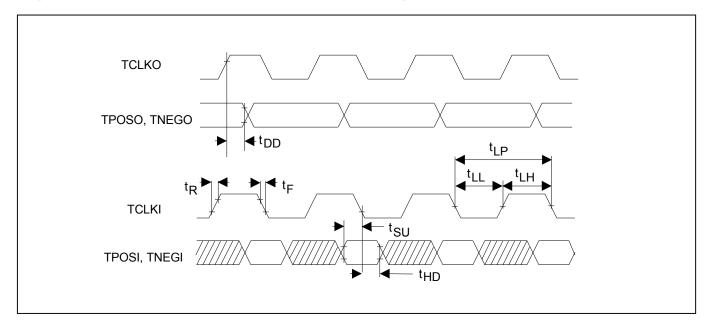

| 37.                                  | AC TIMING PARAMETERS AND DIAGRAMS                                                                                                                                                   | 224               |

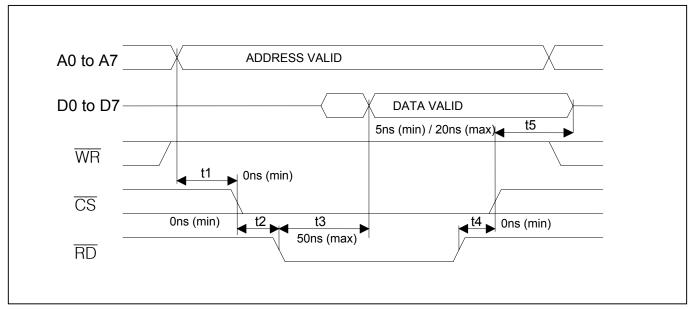

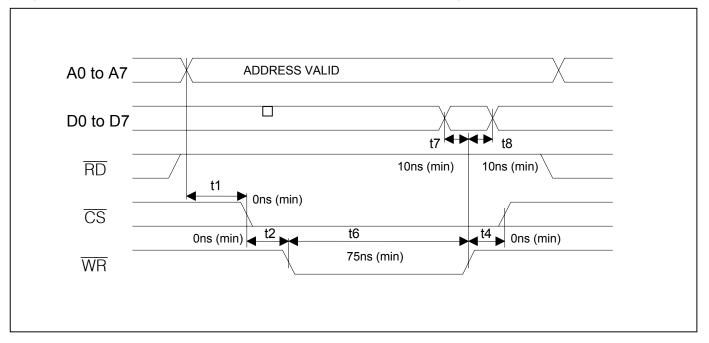

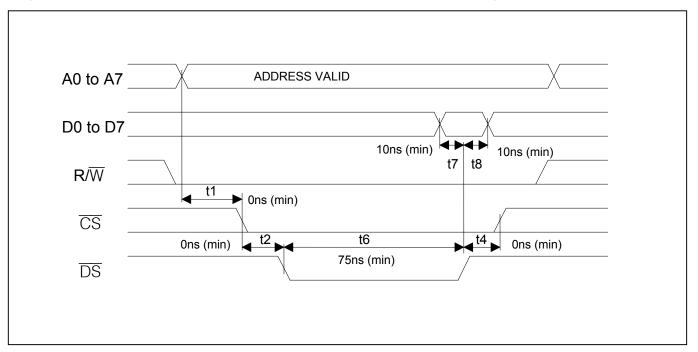

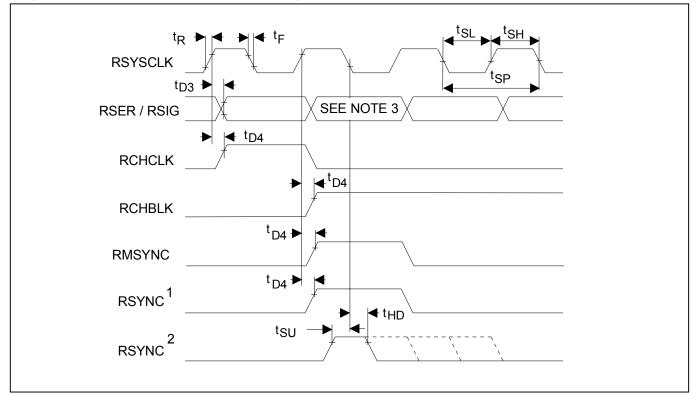

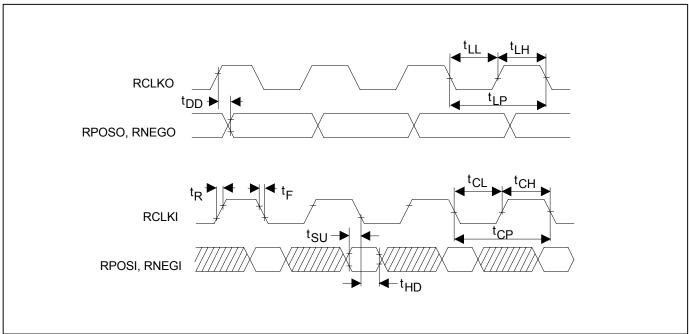

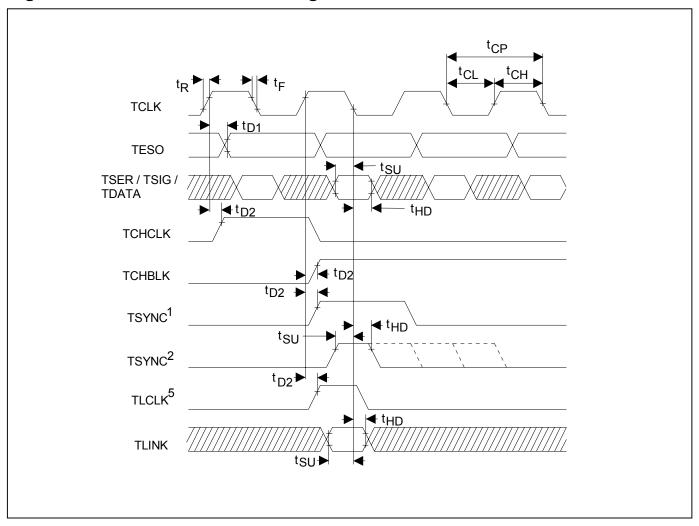

| 37.1<br>37.2<br>37.3<br>37.4<br>37.5 | MULTIPLEXED BUS AC CHARACTERISTICS  NONMULTIPLEXED BUS AC CHARACTERISTICS  RECEIVE-SIDE AC CHARACTERISTICS  BACKPLANE CLOCK TIMING: AC CHARACTERISTICS  TRANSMIT AC CHARACTERISTICS | 227<br>230<br>233 |

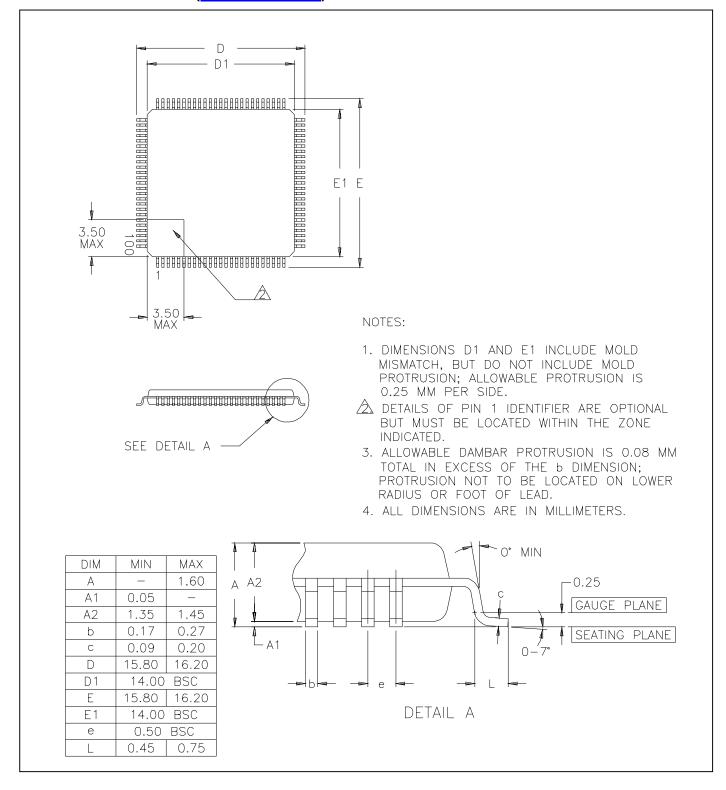

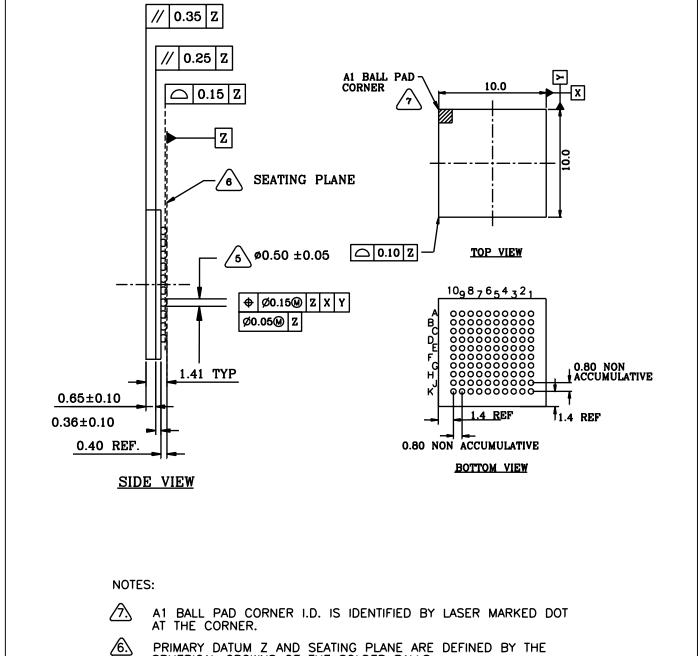

| 38.                                  | PACKAGE INFORMATION                                                                                                                                                                 |                   |

| 38.1<br>38.2                         | 100-PIN LQFP ( <u>56-G5002-000</u> )                                                                                                                                                | 237               |

# 1.1 Table of Figures

| Figure 3-1. Block Diagram                                                               | 15  |

|-----------------------------------------------------------------------------------------|-----|

| Figure 3-2. Receive and Transmit LIU                                                    |     |

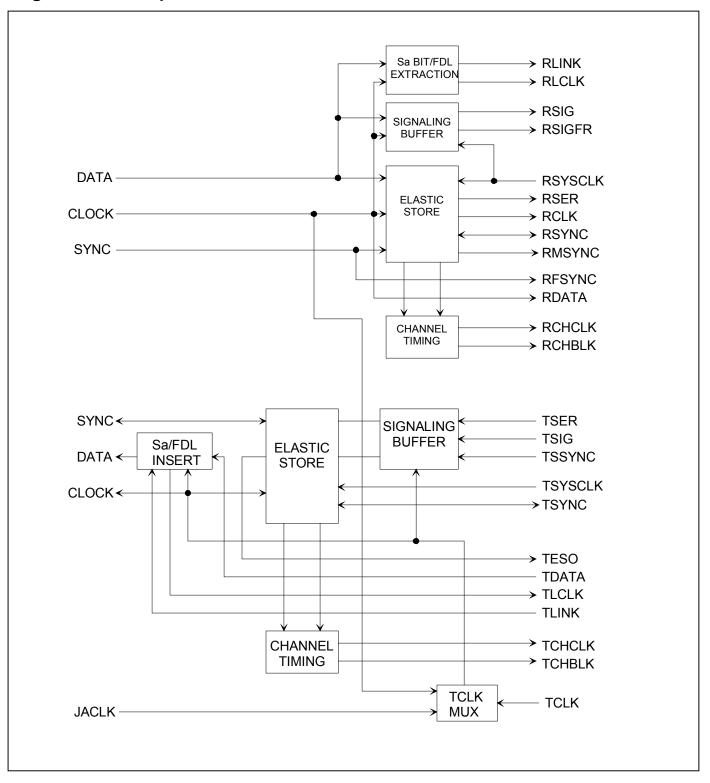

| Figure 3-3. Receive and Transmit Framer/HDLC                                            | 17  |

| Figure 3-4. Backplane Interface                                                         | 18  |

| Figure 4-1. 10mm CSBGA Pin Configuration                                                | 32  |

| Figure 6-1. Programming Sequence                                                        | 39  |

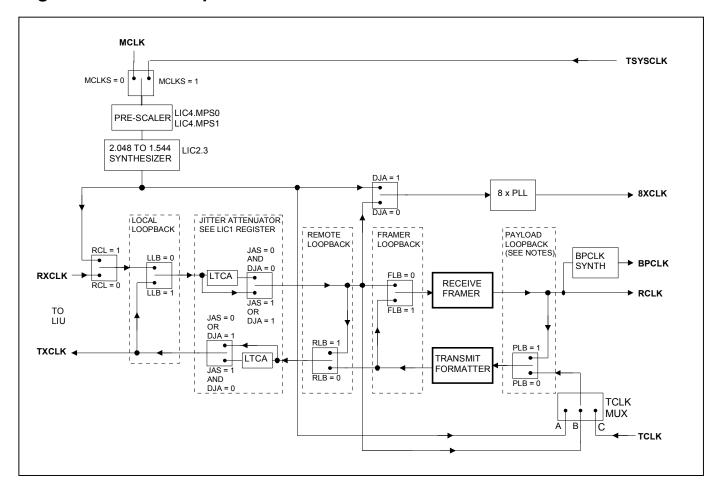

| Figure 8-1. Clock Map                                                                   | 45  |

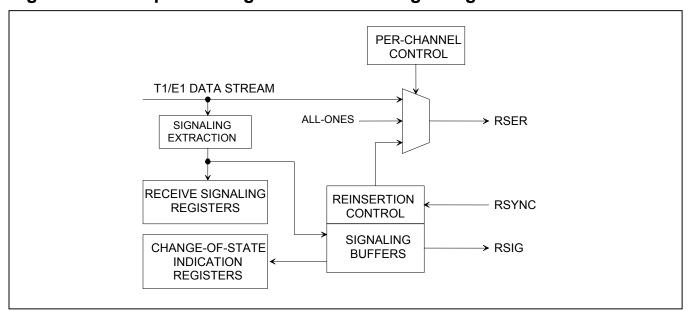

| Figure 16-1. Simplified Diagram of Receive Signaling Path                               | 83  |

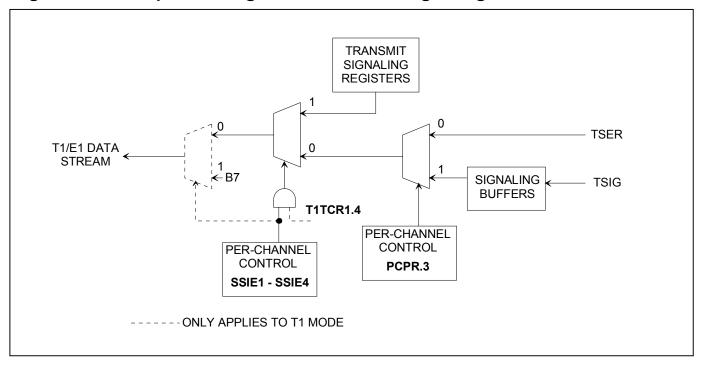

| Figure 16-2. Simplified Diagram of Transmit Signaling Path                              | 89  |

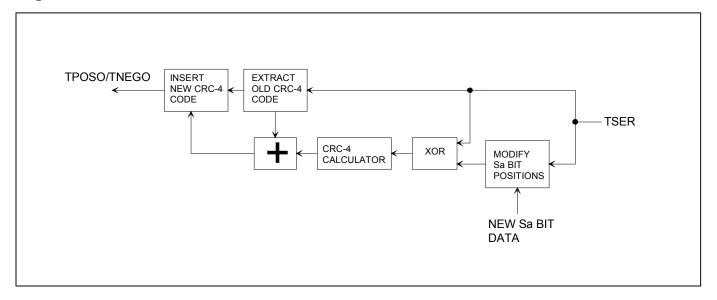

| Figure 20-1. CRC-4 Recalculate Method                                                   | 109 |

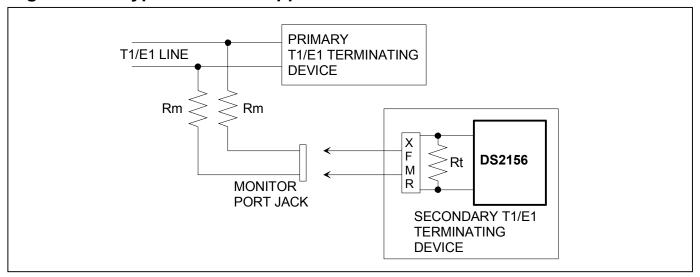

| Figure 24-1. Typical Monitor Application                                                | 144 |

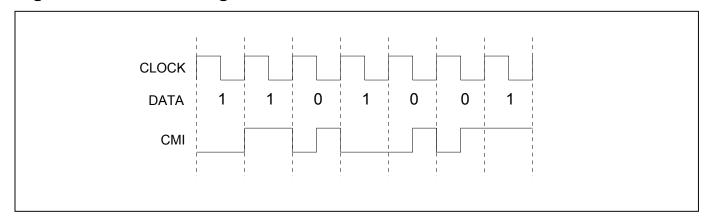

| Figure 24-2. CMI Coding                                                                 | 146 |

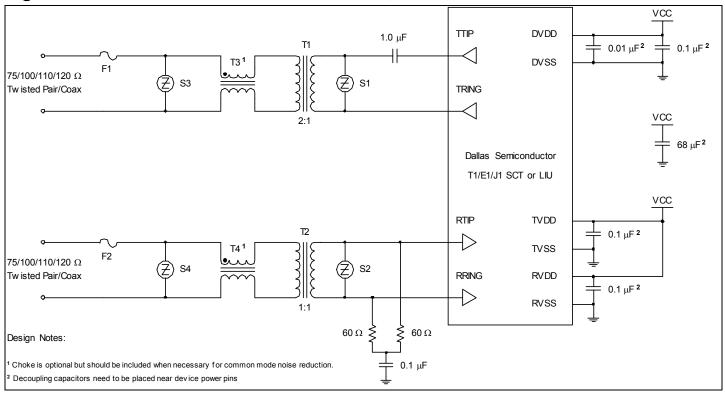

| Figure 24-3. Software-Selected Termination, Metallic Protection                         | 156 |

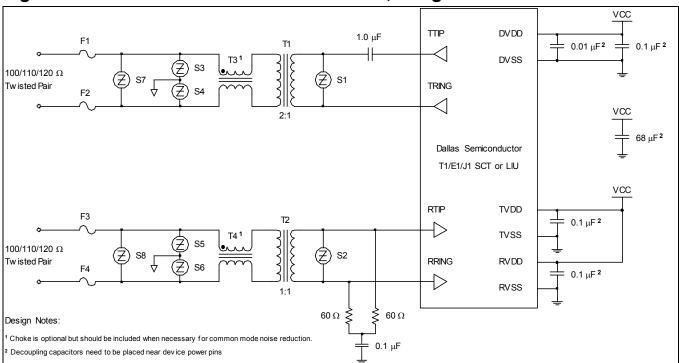

| Figure 24-4. Software-Selected Termination, Longitudinal Protection                     | 157 |

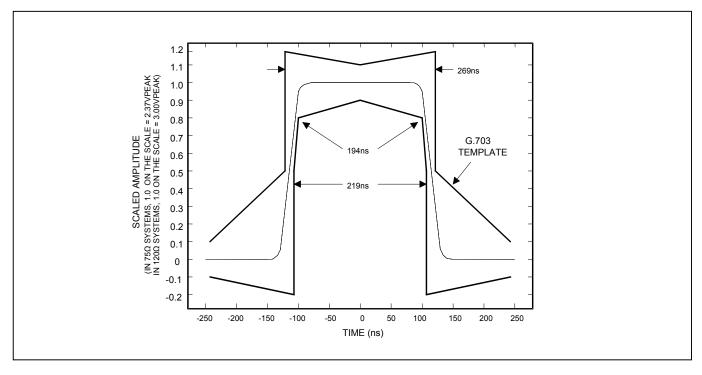

| Figure 24-5. E1 Transmit Pulse Template                                                 | 159 |

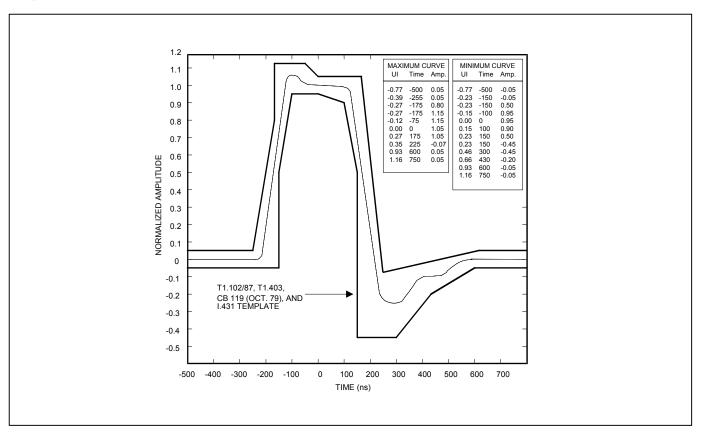

| Figure 24-6. T1 Transmit Pulse Template                                                 | 159 |

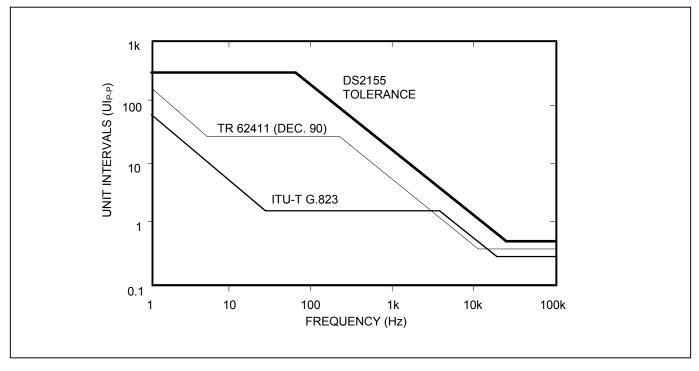

| Figure 24-7. Jitter Tolerance                                                           | 160 |

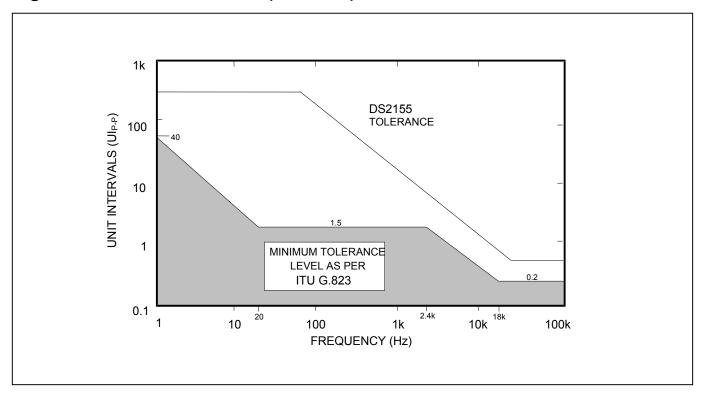

| Figure 24-8. Jitter Tolerance (E1 Mode)                                                 | 160 |

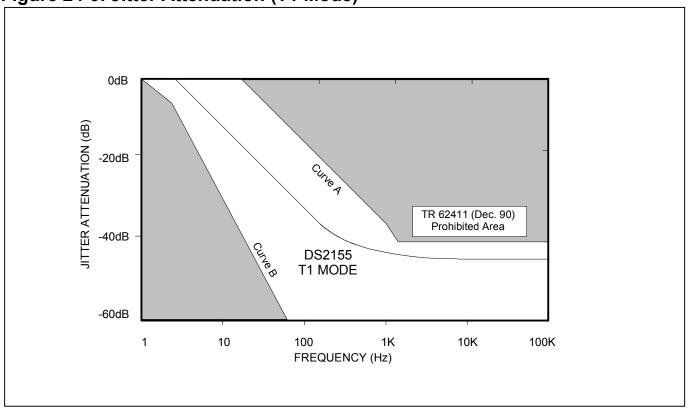

| Figure 24-9. Jitter Attenuation (T1 Mode)                                               | 161 |

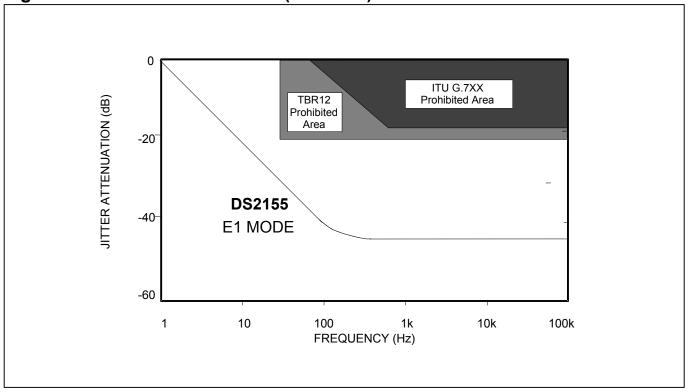

| Figure 24-10. Jitter Attenuation (E1 Mode)                                              | 161 |

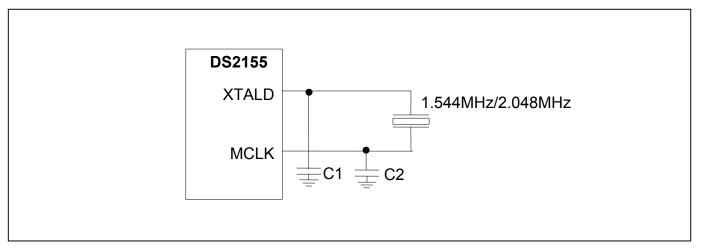

| Figure 24-11. Optional Crystal Connections                                              | 162 |

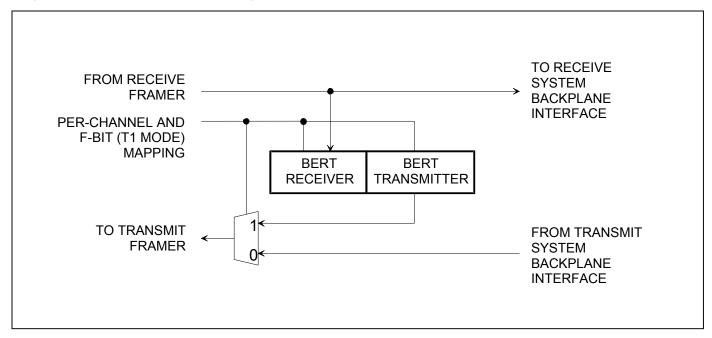

| Figure 26-1. Simplified Diagram of BERT in Network Direction                            | 171 |

| Figure 26-2. Simplified Diagram of BERT in Backplane Direction                          | 171 |

| Figure 28-1. IBO Example                                                                | 186 |

| Figure 29-1. ESIB Group of Four DS2155s                                                 | 187 |

| Figure 33-1. T1 Transmit Flow Diagram                                                   | 194 |

| Figure 33-2. E1 Transmit Flow Diagram                                                   | 195 |

| Figure 34-1. JTAG Functional Block Diagram                                              | 199 |

| Figure 34-2. TAP Controller State Diagram                                               | 202 |

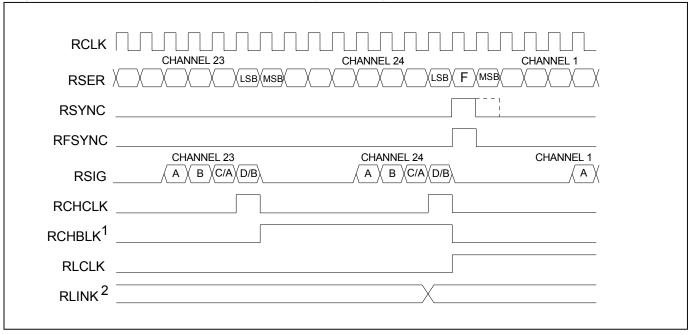

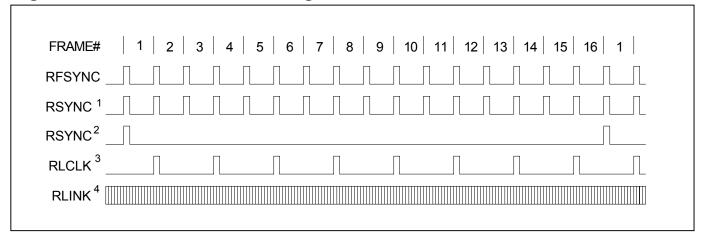

| Figure 35-1. Receive-Side D4 Timing                                                     |     |

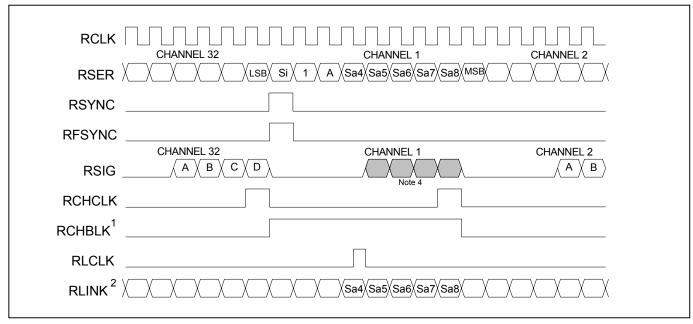

| Figure 35-2. Receive-Side ESF Timing                                                    |     |

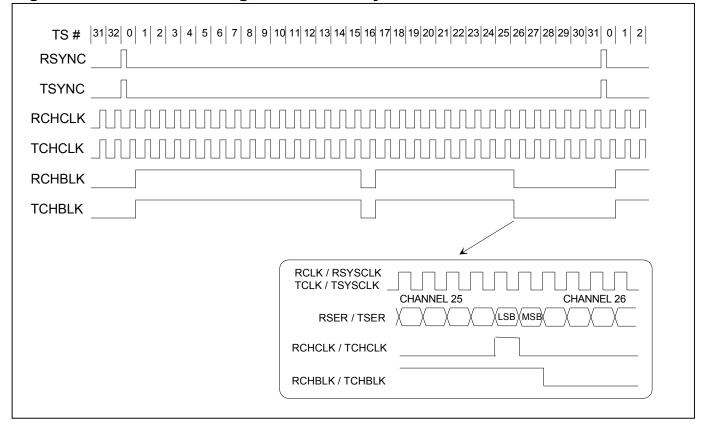

| Figure 35-3. Receive-Side Boundary Timing (Elastic Store Disabled)                      |     |

| Figure 35-4. Receive-Side 1.544MHz Boundary Timing (Elastic Store Enabled)              |     |

| Figure 35-5. Receive-Side 2.048MHz Boundary Timing (Elastic Store Enabled)              |     |

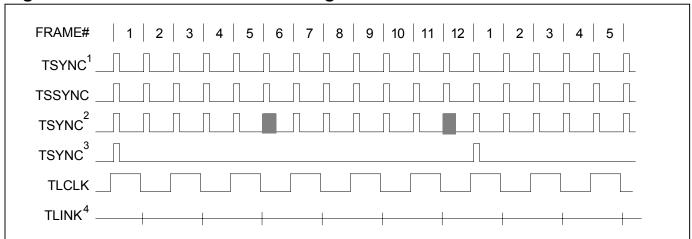

| Figure 35-6. Transmit-Side D4 Timing                                                    |     |

| Figure 35-7. Transmit-Side ESF Timing                                                   |     |

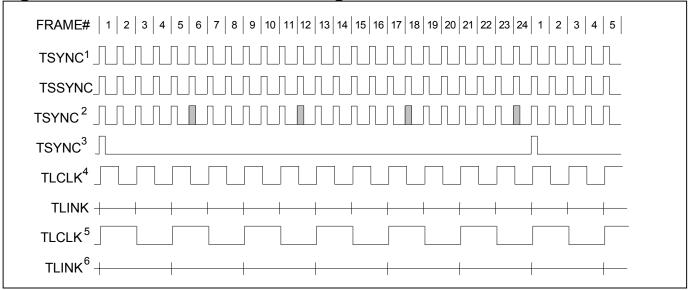

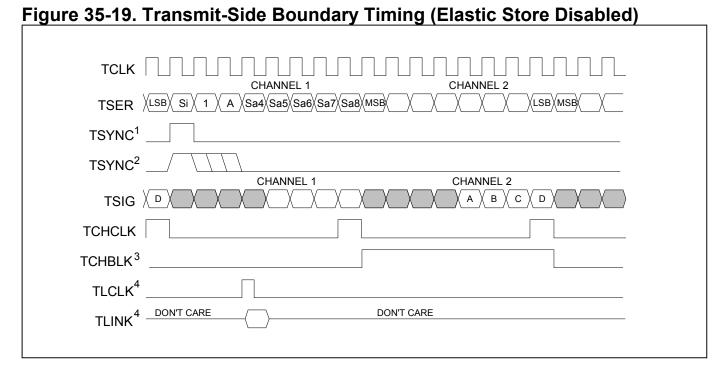

| Figure 35-8. Transmit-Side Boundary Timing (with Elastic Store Disabled)                |     |

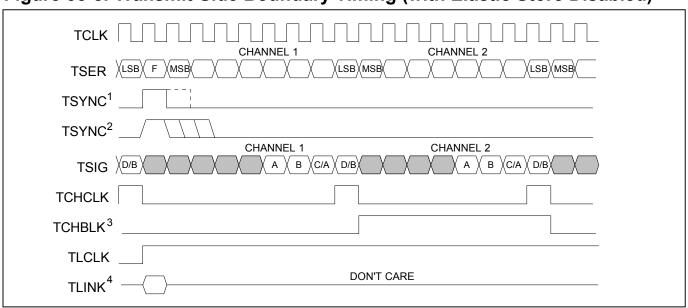

| Figure 35-9. Transmit-Side 1.544MHz Boundary Timing (Elastic Store Enabled)             |     |

| Figure 35-10. Transmit-Side 2.048MHz Boundary Timing (Elastic Store Enabled)            |     |

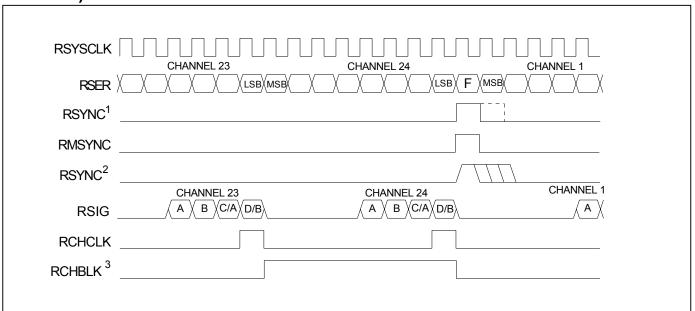

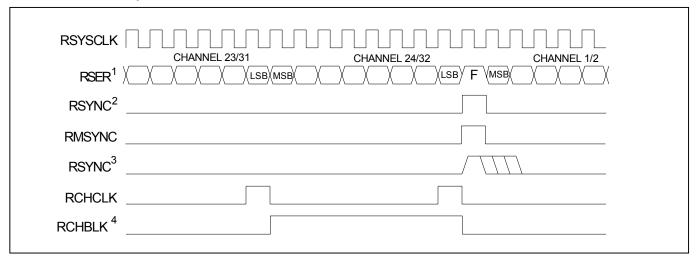

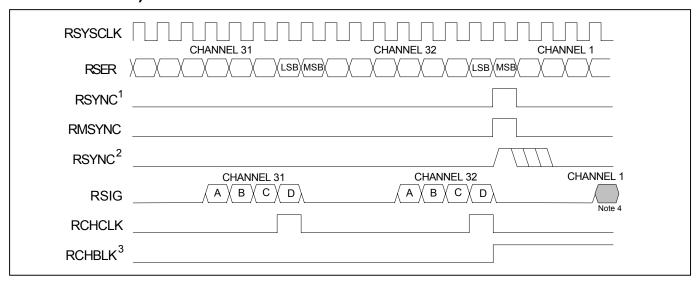

| Figure 35-11. Receive-Side Timing                                                       |     |

| Figure 35-12. Receive-Side Boundary Timing (with Elastic Store Disabled)                |     |

| Figure 35-13. Receive-Side Boundary Timing, RSYSCLK = 1.544MHz (Elastic Store Enabled)  |     |

| Figure 35-14. Receive-Side Boundary Timing, RSYSCLK = 2.048MHz (Elastic Store Enabled)  |     |

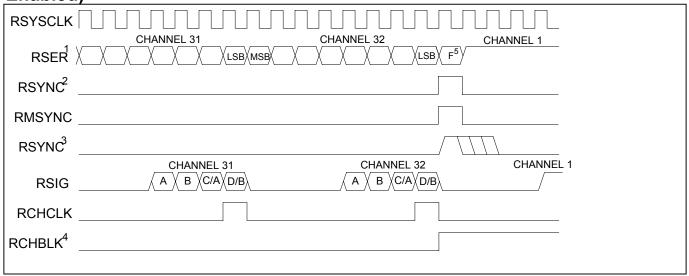

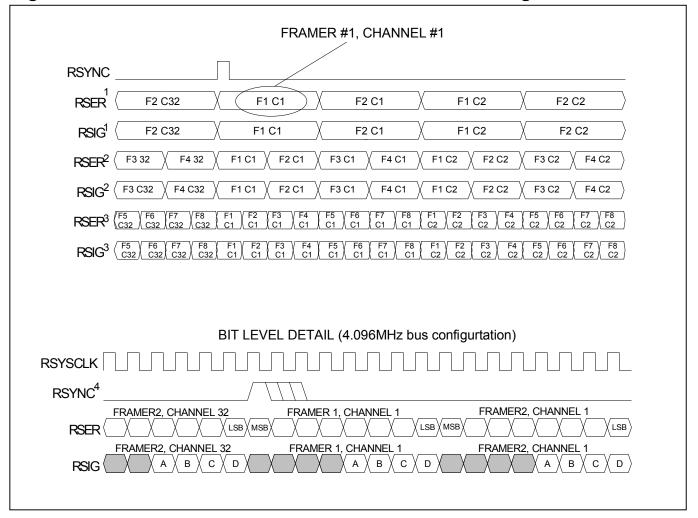

| Figure 35-15. Receive IBO Channel Interleave Mode Timing                                |     |

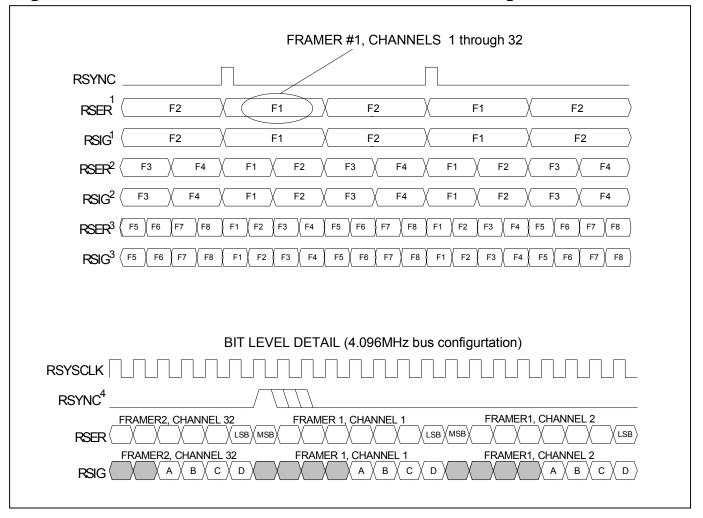

| Figure 35-16. Receive IBO Frame Interleave Mode Timing                                  |     |

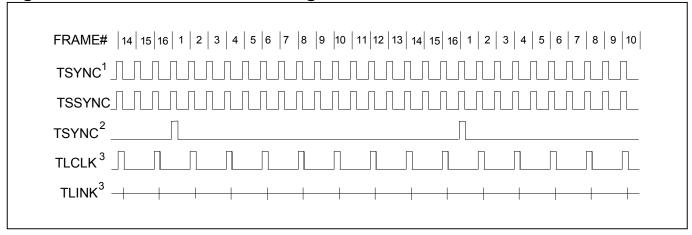

| Figure 35-17. G.802 Timing, E1 Mode Only                                                |     |

| Figure 35-18. Transmit-Side Timing                                                      |     |

| Figure 35-19. Transmit-Side Boundary Timing (Elastic Store Disabled)                    |     |

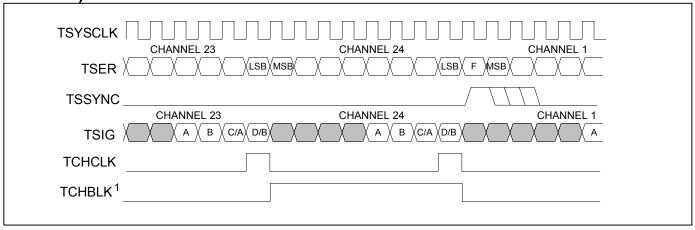

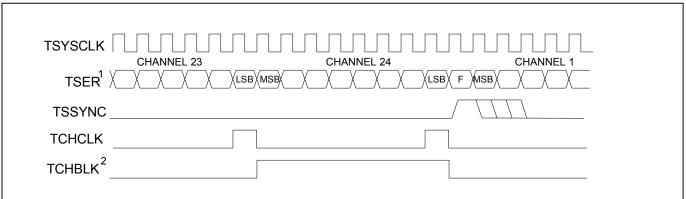

| Figure 35-20. Transmit-Side Boundary Timing, TSYSCLK = 1.544MHz (Elastic Store Enabled) |     |

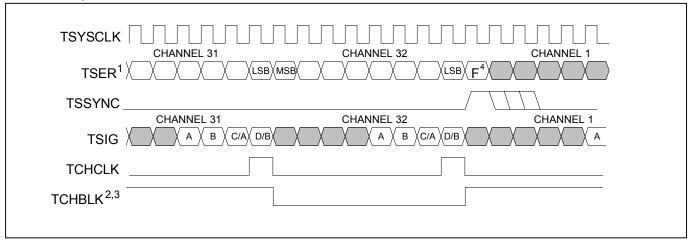

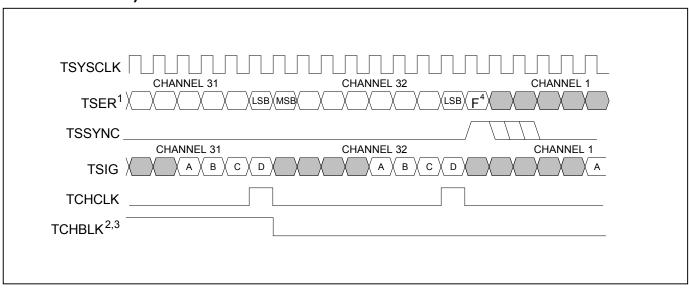

| Figure 35-21. Transmit-Side Boundary Timing, TSYSCLK = 2.048MHz (Elastic Store Enabled) |     |

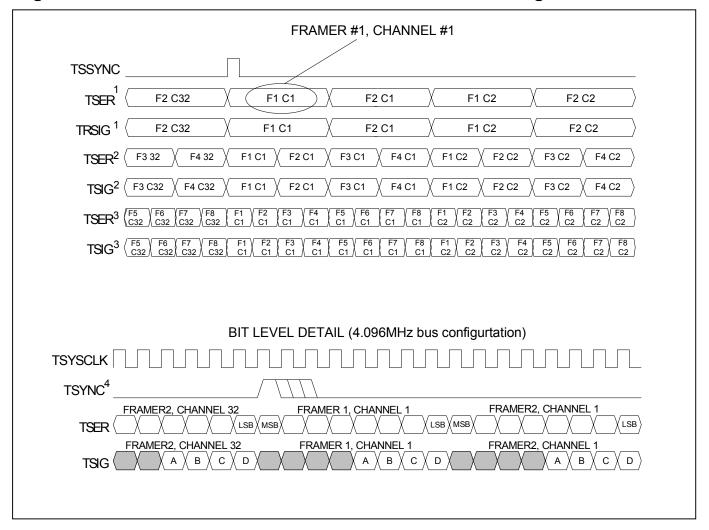

| Figure 35-22 Transmit IRO Channel Interleave Mode Timing                                | 220 |

| Figure 35-23. Transmit IBO Frame Interleave Mode Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 221 |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|--|

| Figure 37-1. Intel Multiplexed Bus Read Timing (BTS = 0/MUX = 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |  |  |  |  |

| Figure 37-2. Intel Multiplexed Bus Write Timing (BTS = 0/MUX = 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |  |  |  |  |

| Figure 37-3. Motorola Multiplexed Bus Timing (BTS = 1/MUX = 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |  |  |

| Figure 37-3. Motorola Multiplexed Bus Timing (BTS = 1/MUX = 1).  Figure 37-4. Intel Nonmultiplexed Bus Read Timing (BTS = 0/MUX = 0).  Figure 37-5. Intel Nonmultiplexed Bus Write Timing (BTS = 0/MUX = 0).  Figure 37-6. Motorola Nonmultiplexed Bus Read Timing (BTS = 1/MUX = 0).  Figure 37-7. Motorola Nonmultiplexed Bus Write Timing (BTS = 1/MUX = 0).  Figure 37-8. Receive-Side Timing.  Figure 37-9. Receive-Side Timing, Elastic Store Enabled.  Figure 37-10. Receive Line Interface Timing.  Figure 37-11. Receive Timing Delay RCLK to BPCLK.  Figure 37-12. Transmit-Side Timing, Elastic Store Enabled.  Figure 37-13. Transmit-Side Timing, Elastic Store Enabled.  Figure 37-14. Transmit Line Interface Timing.   1.2 Table of Tables  Table 4-A. Pin Description Sorted by Pin Number.  Table 5-A. Register Map Sorted by Address.  Table 10-A. E1 Sync/Resync Criteria.  Table 10-B. E1 Alarm Criteria.  Table 14-B. E1 Line-Code Violation Counting Options.  Table 14-C. T1 Path Code Violation Counting Arrangements.  Table 14-D. T1 Frames Out-of-Sync Counting Arrangements. |     |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |  |  |

| G.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |  |  |

| Table 16-A. Time Slot Numbering Schemes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |  |  |  |  |

| Table 17-A. Idle-Code Array Address Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |  |  |  |  |

| Table 19-A. Elastic Store Delay After Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |  |  |  |  |

| Table 23-A. HDLC Controller Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |  |  |  |  |

| Table 24-A. Component List (Software-Selected Termination, Metallic Protection)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |  |  |

| Table 24-B. Component List (Software-Selected Termination, Nettanic Frotection)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |  |  |

| Table 24-C. Transformer Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |  |  |  |  |

| Table 27-A. Transmit Error-Insertion Setup Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |  |  |  |  |

| Table 27-B. Error Insertion Examples.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |  |  |  |  |

| Table 34-A. Instruction Codes for IEEE 1149.1 Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |  |  |  |  |

| Table 34-B. ID Code Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |  |  |  |  |

| Table 34-C. Device ID Codes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |  |  |  |  |

| Table 34-D. Boundary Scan Control Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 205 |  |  |  |  |

# 2. DATA SHEET REVISION HISTORY

| REVISION | DESCRIPTION                                                                                                                                                                                 |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | In Section 3: Line Interface and Section 3.1: Functional Description, corrected dB values                                                                                                   |

| 080607   | for E1 and T1 (page 10 and page 13):                                                                                                                                                        |

| 080007   | E1: 0 to -43dB and 0 to -12dB                                                                                                                                                               |

|          | T1: 0 to -15dB and 0 to -36dB                                                                                                                                                               |

| 040907   | Added Note 1 (GBD for cold temp) to Absolute Maximum Ratings (Section 36).                                                                                                                  |

| 041806   | Replaced Figure 24-3 and Figure 24-4, added Table 24-A and Table 24-B.                                                                                                                      |

| 011606   | Added lead-free packages to Ordering Information table on page 1.                                                                                                                           |

| 100903   | Add revision history table: The previous version of the DS2155 data sheet (12-06-02) did                                                                                                    |

|          | not incorporate a revision history table and did not describe new features added to B1                                                                                                      |

|          | revision of the DS2155.                                                                                                                                                                     |

|          | THE FOLLOWING WERE INADVERTENTLY REMOVED FROM THE                                                                                                                                           |

|          | PREVIOUS VERSION OF THE DS2155 DATA SHEET:                                                                                                                                                  |

|          | Add CSBGA package information to Ordering Information table on front page                                                                                                                   |

|          | Add CSBGA package thermal characteristics to Operating Parameters section                                                                                                                   |

|          | Add Transmit Line Build Out Control register (TLBC) description                                                                                                                             |

|          | Add Transmit Line Build Out Control register (TLBC) to Port Map                                                                                                                             |

|          | Add Transmit Line Build Out Control register (TLBC) description to LIU TRANSMIT                                                                                                             |

|          | section                                                                                                                                                                                     |

|          |                                                                                                                                                                                             |

|          | THE FOLLOWING ARE CORRECTIONS TO ERRORS IN THE PREVIOUS VERSION OF THE DS2155 DATA SHEET:                                                                                                   |

|          | Correct Device ID in Device Identification Register                                                                                                                                         |

|          | Correct Device ID in JTAG ID Code table                                                                                                                                                     |

|          | Correct minimum value for t <sub>DHW</sub> in AC CHARACTERISTICS: MULTIPLEXED                                                                                                               |

|          | PARALLEL PORT table. t <sub>DHW</sub> was changed from 5ns to 0ns                                                                                                                           |

|          | Correct minimum value for t <sub>DDR</sub> in AC CHARACTERISTICS: MULTIPLEXED                                                                                                               |

|          | PARALLEL PORT table. t <sub>DDR</sub> was changed from unstated to 20ns                                                                                                                     |

|          | Corrections to AC CHARACTERISTICS: TRANSMIT SIDE timing table.                                                                                                                              |

|          | 1. t <sub>CP</sub> , t <sub>CH</sub> , t <sub>CL</sub> , t <sub>LP</sub> , t <sub>LH</sub> , t <sub>LL</sub> , and t <sub>SP</sub> typical values have been restated to reflect various IBO |

|          | modes.                                                                                                                                                                                      |

|          | 2. t <sub>CH</sub> , t <sub>CL</sub> , t <sub>LH</sub> , t <sub>LL</sub> minimum values have been changed from 75ns to 20ns.                                                                |

|          | 3. t <sub>SP</sub> , t <sub>LL</sub> minimum values have been changed from 50ns to 20ns.                                                                                                    |

|          | 4. t <sub>D3</sub> minimum values have been changed from 75ns to 22ns.                                                                                                                      |

|          | Corrections to AC CHARACTERISTICS: RECEIVE SIDE timing table.                                                                                                                               |

|          | 1. t <sub>CP</sub> , t <sub>CH</sub> , t <sub>CL</sub> , t <sub>LP</sub> , t <sub>LH</sub> , t <sub>LL</sub> , and t <sub>SP</sub> typical values have been restated to reflect various IBO |

|          | modes.                                                                                                                                                                                      |

|          | 2. t <sub>CH</sub> , t <sub>CL</sub> , minimum values have been changed from 75ns to 20ns.                                                                                                  |

|          | 3. t <sub>SH</sub> , t <sub>SL</sub> minimum values have been changed from 50ns to 20ns.                                                                                                    |

|          | 4. t <sub>SH</sub> , t <sub>SL</sub> typical values have been added.                                                                                                                        |

|          | 5. t <sub>D3</sub> , t <sub>D4</sub> minimum values have been changed from 50ns to 22ns.                                                                                                    |

|          | Correct Transmit Signaling Registers (E1 Mode, CCS Format) table in Transmit Signaling                                                                                                      |

|          | section                                                                                                                                                                                     |

| REVISION | DESCRIPTION                                                                                                      |

|----------|------------------------------------------------------------------------------------------------------------------|

|          | The definition of the EGL bit in the LIC1 register has been corrected for both T1 and E1                         |

|          | mode.                                                                                                            |

|          | T1 Mode: EGL = 1 was changed from 15dB to -15dB                                                                  |

|          | E1 Mode: $EGL = 0$ was changed from $-10dB$ to $-12dB$                                                           |

|          |                                                                                                                  |

|          | THE FOLLOWING ARE FORMAT CHANGES AND ADDED OR REMOVED TEXT, TABLES OR DIAGRAMS:                                  |

|          | Replace $X^*$ format for showing active low signals with $\overline{X}$                                          |

|          | Remove redundant statements about "multiport configurations" in Interrupt Handling section                       |

|          | Remove BASIC NETWORK CONNECTIONS figure in LINE INTERFACE UNIT section                                           |

|          | Add "Simplified Diagram of BERT in Network Direction" figure to BERT section                                     |

|          | Add "Simplified Diagram of BERT in Backplane Direction" figure to BERT section                                   |

|          | Add Receive Signaling Registers (E1 Mode, CCS Format) table to Receive Signaling                                 |

|          | section                                                                                                          |

|          | Add GRIC and GTIC function table to IAAR register                                                                |

|          | Changed Table of contents to include table of figures and table of tables.                                       |

|          | Add note for FASRC bit.                                                                                          |

|          | Add T1 and E1 Transmit Flow Chart.                                                                               |

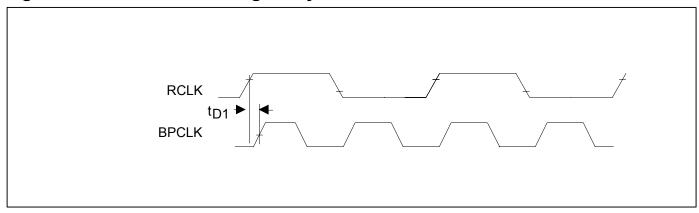

|          | Added RCLK to BPCLK timing diagram.                                                                              |

|          |                                                                                                                  |

|          | THE FOLLOWING ARE NEW FEATURES AVAILABLE ON THE DS2155 REV<br>B1 AND ARE EXPLAINED IN THE BODY OF THE DATA SHEET |

|          | Add FRAS0, TCCS, RCCS and GRSRE bits to Signaling Control Register (SIGCR)                                       |